Samsungin odotetaan kertovan ensi viikolla 3 nanometrin tuotantoprosessin käyttöönotosta massatuotannossa, kertoo Yonhap News.

Lähtökohtaisesti pienempi viivanleveys merkitsee parempaa energiatehokkuutta ja virrankulutusta sekä kääntäen parempaa suorituskykyä muun muassa korkeampien kellotaajuuksien mahdollistumisen kautta. Samanaikaisesti viivanleveyden pienentäminen käy jatkuvasti vaikeammaksi vaatien entistä hienostuneempia rakenteellisia ja tuotannollisia ratkaisuja.

MAINOS (ARTIKKELI JATKUU ALLA)

Samsung on ainakin näennäisesti edellä kilpailevaa TSMC:tä 3 nanometrin käyttöönotossa. TSMC on ottamassa oman 3 nanometrin prosessinsa käyttöön myös vielä alkaen vuoden 2022 aikana.

Käytännössä eri prosessit eivät kuitenkaan ole tekniseltä kehitykseltään välttämättä täysin vertailukelpoisia.

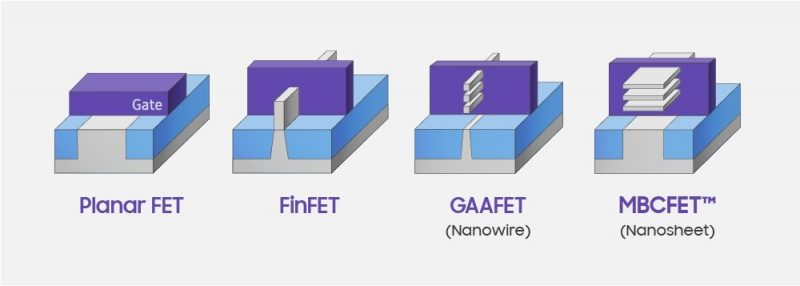

3 nanometrin prosessissa transistorirakenteessa hyödynnetään uutta Gate-All-Around (GAA) -mallia, joka on mahdollistanut koon pienentämisen.

MAINOS (ARTIKKELI JATKUU ALLA)

Vuonna 2023 Samsungilta odotetaan toisen sukupolven 3 nanometrin prosessia ja vuonna 2025 on puolestaan 2 nanometriin siirtymisen vuoro MCBFET-transistorirakenteen kera. Myös TMSMC:n tähtäin 2 nanometrin osalta on vuodessa 2025.

Mainos: Noin 1 600 000 tuotteen hintavertailu ja hintaseuranta - katso Hinta.fistä mistä saat halvimmalla

Salasana hukassa?

Etkö ole vielä rekisteröitynyt? Rekisteröidy tästä »